# Quick Start Guide for Xilinx Alliance Series vM1.3

Introduction

Installation

Core Technology Tutorial

How This Release Works

Cadence Interface Notes

FPGA Express Interface Notes

Mentor Graphics Interface Notes

Synopsys Interface Notes

Viewlogic Interface Notes

LogiBLOX

**Instantiated Components**

M1 Constraints Guide

The Xilinx logo shown above is a registered trademark of Xilinx, Inc.

XILINX, XACT, XC2064, XC3090, XC4005, XC5210, XC-DS501, FPGA Architect, FPGA Foundry, NeoCAD, NeoCAD EPIC, NeoCAD PRISM, NeoROUTE, Plus Logic, Plustran, P+, Timing Wizard, and TRACE are registered trademarks of Xilinx, Inc.

The shadow X shown above is a trademark of Xilinx, Inc.

All XC-prefix product designations, XACTstep, XACTstep Advanced, XACTstep Foundry, XACT-Floorplanner, XACT-Performance, XAPP, XAM, X-BLOX, X-BLOX plus, XChecker, XDM, XDS, XEPLD, XPP, XSI, BITA, Configurable Logic Cell, CLC, Dual Block, FastCLK, FastCONNECT, FastFLASH, FastMap, HardWire, LCA, LogiBLOX, Logic Cell, LogicCORE, LogicProfessor, MicroVia, PLUSASM, PowerGuide, PowerMaze, Select-RAM, SMARTswitch, TrueMap, UIM, VectorMaze, VersaBlock, VersaRing, XABEL, Xilinx Foundation Series, and ZERO+ are trademarks of Xilinx, Inc. The Programmable Logic Company and The Programmable Gate Array Company are service marks of Xilinx, Inc.

IBM is a registered trademark and PC/AT, PC/XT, PS/2 and Micro Channel are trademarks of International Business Machines Corporation. DASH, Data I/O and FutureNet are registered trademarks and ABEL, ABEL-HDL and ABEL-PLA are trademarks of Data I/O Corporation. SimuCad and Silos are registered trademarks and P-Silos and P/C-Silos are trademarks of SimuCad Corporation. Microsoft is a registered trademark and MS-DOS is a trademark of Microsoft Corporation. Centronics is a registered trademark of Centronics Data Computer Corporation. PALASM is a registered trademark of Advanced Micro Devices, Inc. UNIX is a trademark of AT&T Technologies, Inc. CUPL, PROLINK, and MAKEPRG are trademarks of Logical Devices, Inc. Apollo and AEGIS are registered trademarks of Hewlett-Packard Corporation. Mentor and IDEA are registered trademarks and NETED, Design Architect, System Architect, QuickSim, QuickSim II, and EXPAND are trademarks of Mentor Graphics, Inc. Sun is a registered trademark of Sun Microsystems, Inc. SCHEMA II+ and SCHEMA III are trademarks of Omation Corporation. OrCAD is a registered trademark of OrCAD Systems Corporation. Viewlogic, Viewsim, and Viewdraw are registered trademarks of Viewlogic Systems, Inc. CASE Technology is a trademark of CASE Technology, a division of the Teradyne Electronic Design Automation Group. DECstation is a trademark of Digital Equipment Corporation. Synopsys is a registered trademark of Synopsys, Inc. Verilog is a registered trademark of Cadence Design Systems, Inc. FLEXIm is a trademark of Globetrotter, Inc. DynaText is a registered trademark of Inso Corporation.

Xilinx, Inc. does not assume any liability arising out of the application or use of any product described or shown herein; nor does it convey any license under its patents, copyrights, or maskwork rights or any rights of others. Xilinx, Inc. reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx, Inc. will not assume responsibility for the use of any circuitry described herein other than circuitry entirely embodied in its products. Xilinx, Inc. devices and products are protected under one or more of the following U.S. Patents: 4,642,487; 4,695,740; 4,706,216; 4,713,557; 4,746,822; 4,750,155; 4,758,985; 4,820,937; 4,821,233; 4,835,418; 4,853,626; 4,855,619; 4,855,669; 4,902,910; 4,940,909; 4,967,107; 5,012,135; 5,023,606; 5,028,821; 5,047,710; 5,068,603; 5,140,193; 5,148,390; 5,155,432; 5,166,858; 5,224,056; 5,243,238; 5,245,277; 5,267,187; 5,291,079; 5,295,090; 5,302,866; 5,319,252; 5,319,254; 5,321,704; 5,329,174; 5,329,181; 5,331,220; 5,331,226; 5,332,929; 5,337,255; 5,343,406; 5,349,248; 5,349,249; 5,349,250; 5,349,691;

5,357,153; 5,360,747; 5,361,229; 5,362,999; 5,365,125; 5,367,207; 5,386,154; 5,394,104; 5,399,924; 5,399,925; 5,410,189; 5,410,194; 5,414,377; 5,422,833; 5,426,378; 5,426,379; 5,430,687; 5,432,719; 5,448,181; 5,448,493; 5,450,021; 5,450,022; 5,453,706; 5,466,117; 5,469,003; 5,475,253; 5,477,414; 5,481,206; 5,483,478; 5,486,707; 5,486,776; 5,488,316; 5,489,858; 5,489,866; 5,491,353; 5,495,196; 5,498,979; 5,498,989; 5,499,192; 5,500,608; 5,500,609; 5,502,000; 5,502,440; RE 34,363, RE 34,444, and RE 34,808. Other U.S. and foreign patent pending. Xilinx, Inc. does not represent that devices shown or products described herein are free from patent infringement or from any other third party right. Xilinx, Inc. assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made. Xilinx, Inc. will not assume any liability for the accuracy or correctness of any engineering or software support or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the written consent of the appropriate Xilinx officer is prohibited.

Copyright 1991-1997 Xilinx, Inc. All Rights Reserved.

#### Glossary

#### **Preface**

#### **About This Manual**

This quick start guide does what its title purports, provides an overview of the features and additions to Xilinx's newest product: vM1.3 Software. The primary focus of this guide is the Core Technology tools used to implement a design.

#### **Manual Contents**

This manual covers the following topics.

- Chapter 1, "Introduction," introduces the new and enhanced features of the M1 software.

- Chapter 2, "Installation," gives instructions on the installation of the latest XIlinx software on workstations, and PCs.

- Chapter 3, "Core Technology Tutorial," provides a tutorial which exercises a significant portion of the features of the M1 design flow.

- Chapter 4, "How This Release Works," looks in-depth at the capability and flexibility of the Xilinx software.

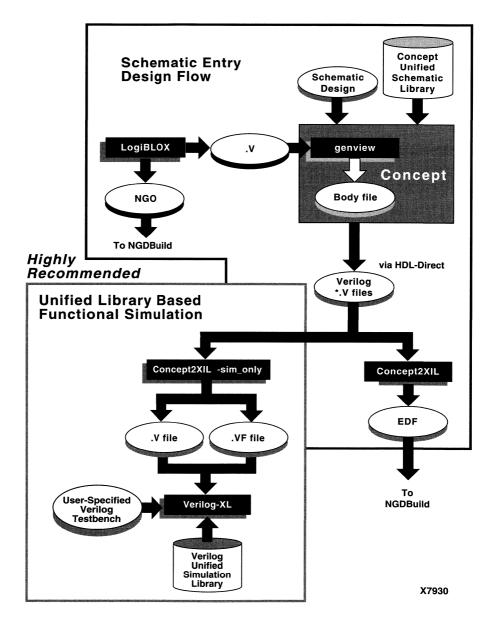

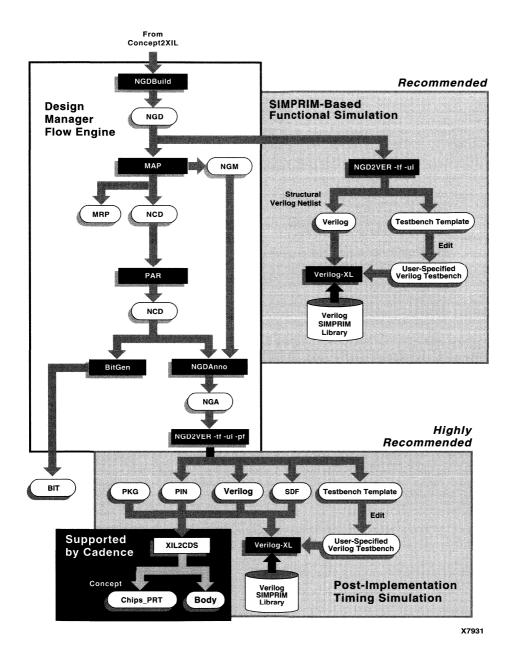

- Appendix A, "Cadence Concept and Verilog Interface Notes," covers how to set up the Cadence Concept interface for schematic entry, and Verilog-XL for simulation.

- Appendix B, "FPGA Express Interface Notes," covers how to install and start using FPGA Express and the XACTstep vM1.3, Synopsis, and the Xilinx CDROM documentation.

- Appendix C, "Mentor Graphics Interface Notes," covers how to set up the Mentor Graphics interface and associated libraries.

- Appendix D, "Synopsys Interface Notes," covers how to set up the Synopsis interface and associated libraries.

- Appendix E, "Viewlogic Interface Notes," covers how to set up the Viewlogic interface and project libraries.

- Appendix F, "LogiBLOX," covers how to set up the LogiBLOX interface and associated libraries

- Appendix G, "Instantiated Components," includes a listing of the components most frequently instantiated in synthesis designs.

- Appendix H, "M1 Constraints Guide," describes the most common constraints you can apply to your design to control the timing and layout of a Xilinx FPGA or CPLD.

- Appendix I, "Glossary," contains definitions and explanations for terms used in the Quick Start Guide.

There are eight appendices, five of them devoted each to an interface, one to LogiBLOX (including HDL), one to frequently instantiated components, and the last features the M1 constraints guide.

#### **Conventions**

This manual uses the following conventions. An example illustrates each convention.

Courier font indicates messages, prompts, and program files that the system displays.

```

speed grade: -100

```

• **Courier bold** indicates literal commands that you enter in a syntactical statement.

```

rpt_del_net=

```

**Courier bold** also indicates commands that you select from a menu.

#### $\mathtt{File} o \mathtt{Open}$

- *Italic font* denotes the following items.

- Variables in a syntax statement for which you must supply values

edif2ngd design\_name

References to other manuals

See the *Development System Reference Guide* for more information.

• Emphasis in text

If a wire is drawn so that it overlaps the pin of a symbol, the two nets are *not* connected.

Square brackets "[]" indicate an optional entry or parameter. However, in bus specifications, such as bus [7:0], they are required. edif2ngd [option\_name] design\_name

Square brackets also enclose footnotes in tables that are printed out as hardcopy in DynaText<sup>®</sup>.

Braces "{ }" enclose a list of items from which you choose one or more.

```

lowpwr = {on|off}

```

• A vertical bar "|" separates items in a list of choices.

```

symbol editor_name [bus|pins]

```

A vertical ellipsis indicates repetitive material that has been omitted.

```

IOB #1: Name = QOUT'

IOB #2: Name = CLKIN'

.

```

• A horizontal ellipsis "..." indicates that an item can be repeated one or more times.

```

allow block block_name loc1 loc2 . . . locn;

```

In addition, Xilinx has created several conventions for use within the DynaText online documents.

- Red-underlined text indicates an interbook link, which is a cross-reference to another book. Click on the red-underlined text to open the specified cross-reference.

- Blue-underlined text indicates an intrabook link, which is a crossreference within a book. Click on the blue-underlined text to open the specified cross-reference.

0

• There are several types of icons.

Iconized figures are identified by the figure icon.

#### Figure 1-1 Naming Conventions

Iconized tables are identified by the table icon.

Table 13-14 Carry Modes

The Copyright icon displays in the upper left corner on the first page of every Xilinx online document.

The DynaText footnote icon displays next to the footnoted text.

#### Масто 52

Double-click on these icons to display figures, tables, copyright information, or footnotes in a separate window.

• Inline figures display within the text of a document. You can display these figures in a separate window by clicking on the figure.

### **Contents**

| Chapter 1 | Introduction                                                                                                                                                                                                                                                                                                                                                                 |                                                                                  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

|           | Introduction M1 Software Supported Families Supported Netlists M1 Software Instruction Volumes New and Enhanced Tools Design Manager Flow Engine LogiBLOX Timing Specification Performance Timing Analyzer Multi-Pass PAR Re-Entrant Routing Guide for Incremental Design Changes EPIC - Physical Design Editor Hardware Debugger PROM File Formatter Third Party Interfaces | 1-1<br>1-2<br>1-2<br>1-3<br>1-3<br>1-3<br>1-4<br>1-4<br>1-5<br>1-5<br>1-6<br>1-6 |

| Chapter 2 | Installation                                                                                                                                                                                                                                                                                                                                                                 |                                                                                  |

|           | Introduction Technical Support Hotline Access Obtaining and Setting Up Licenses Customer Service United States and Canada Europe Other International Countries  Registering and Licensing from the Web                                                                                                                                                                       | 2-2<br>2-2<br>2-2<br>2-4<br>2-4<br>2-4<br>2-4                                    |

|           | To generate a license online, the following information is required: | 2.5  |

|-----------|----------------------------------------------------------------------|------|

|           | 9-Digit End User ID Number (example, 1234-01-01-A)                   |      |

|           | Product Serial Number                                                |      |

|           | Product Type                                                         |      |

|           | Xilinx Web Licensing and Registration Program                        |      |

|           | Registering Via Telephone/Fax                                        |      |

|           | PC or Workstation                                                    |      |

|           | What type of machine will be used as the license                     | 20   |

|           | server: PC or Workstation?                                           | 2-6  |

|           | What type of machine will actually be running the M1                 | 20   |

|           | Core Technology software: PC or Workstation or both?                 | 2-6  |

|           | 3. What type of license is needed: node-locked or                    | 2-0  |

|           | floating?                                                            | 2-7  |

|           | Setting Up Your License File                                         |      |

|           | Workstation Users:                                                   |      |

|           | PC Users:                                                            |      |

|           | M1 Requirements for Workstations                                     |      |

|           | M1 Installation on Workstations                                      |      |

|           | Installing the Core Technology Software                              |      |

|           | Installing the CAE Interface and Libraries                           |      |

|           | Installing the On-line Documentation                                 |      |

|           | Variable Settings for Workstations                                   |      |

|           | Verifying Core Technology Software Installation -                    |      |

|           | Workstations                                                         | 2-11 |

|           | Example 1:                                                           |      |

|           | Example 2:                                                           |      |

|           | Example 3:                                                           |      |

|           | Verifying DynaText Variable Settings - Workstation                   |      |

|           | Setting Up LogiBLOX for Workstations                                 |      |

|           | M1 Requirements for PCs                                              |      |

|           | M1 Installation on PC                                                |      |

|           | Installing Core Technology Software, CAE Interface and               |      |

|           | Libraries                                                            | 2-14 |

|           | Installing Workview Office Toolset                                   |      |

|           | Installing On-line Documentation                                     |      |

|           | Variable Settings for PCs                                            |      |

|           | Setting Up LogiBLOX for Use With Workview Office                     |      |

| Chapter 3 | Core Technology Tutorial                                             |      |

|           | Tutorial Installation                                                | 3-1  |

|           |                                                                      |      |

| Chapter 4  | Step 1: Invoking Design Manager, Creating an Implementation Project | 3-4<br>3-6<br>3-12<br>3-14<br>3-18<br>3-20<br>3-22 |

|------------|---------------------------------------------------------------------|----------------------------------------------------|

| Jilaptei 4 |                                                                     |                                                    |

|            | Starting Xilinx Tools                                               |                                                    |

|            | Creating A Project                                                  |                                                    |

|            | Implementing A Design                                               |                                                    |

|            | Translate                                                           |                                                    |

|            | Map                                                                 |                                                    |

|            | Place and Route                                                     |                                                    |

|            | Configure                                                           |                                                    |

|            | Analyzing Reports  Translation Report                               |                                                    |

|            | Map Report                                                          |                                                    |

|            | Place and Route Report                                              |                                                    |

|            | Pad Report                                                          |                                                    |

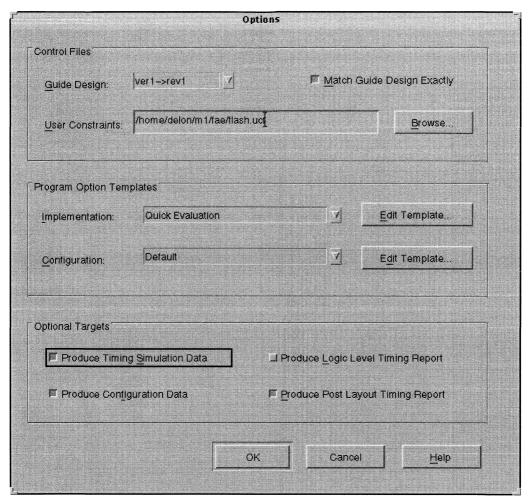

|            | Selecting Options                                                   |                                                    |

|            | Using Constraint Files                                              |                                                    |

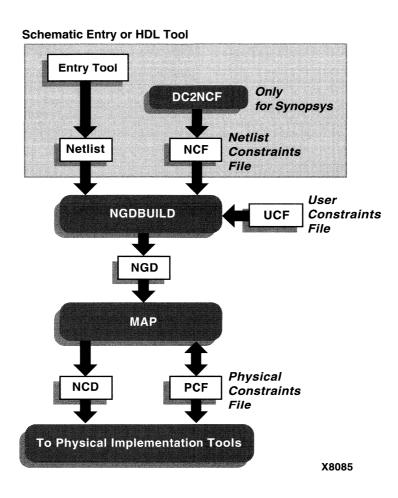

|            | Design, Netlist, User, and Physical Constraints                     |                                                    |

|            | Creating A User Constraint File                                     |                                                    |

|            | Guiding An Implementation                                           |                                                    |

|            | Exact Guide Mode                                                    | 4-115                                              |

|            | Leveraged Guide Mode                                                | 4-115                                              |

|            | Static Timing Analysis                                              | 4-115                                              |

|            | Static Timing Analysis After Map                                    |                                                    |

|            | Static Timing Analysis After Place and Route                        |                                                    |

|            | Summary Timing Reports                                              |                                                    |

|            | Detailed Timing Analysis                                            |                                                    |

|            | Creating Simulation Files                                           |                                                    |

|            | When Can Simulation Data Be Created                                 |                                                    |

|            | Creating Timing Simulation Data                                     |                                                    |

|            | Creating Functional Simulation Data                                 |                                                    |

|            | Downloading A Design                                                | 4-119                                              |

|            | Creating a PROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4-120<br>4-120<br>4-120                                                                           |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| Appendix A | Cadence Concept and Verilog Interface Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                   |

|            | Documentation Setting up the Xilinx/Cadence Interface Cadence/Verilog and M1 Design Flow Setting Up for Concept Using HDL Direct Iterated Instances Vs. Size Support Starting Up Concept Functional Simulation Testfixture: Asserting the Global Set Reset in a Pre-NGDBuild Unified Library Functional Simulation Pure Concept Schematic Functional Simulation Post-NGDBuild Functional Simulation Translating a Design to Xilinx EDIF Timing Simulation Support for Board Level Simulation Pin Locking Timing Constraints | A-2<br>A-4<br>A-8<br>A-10<br>A-10<br>A-11<br>A-11<br>A-11<br>A-13<br>A-14<br>A-14<br>A-15<br>A-15 |

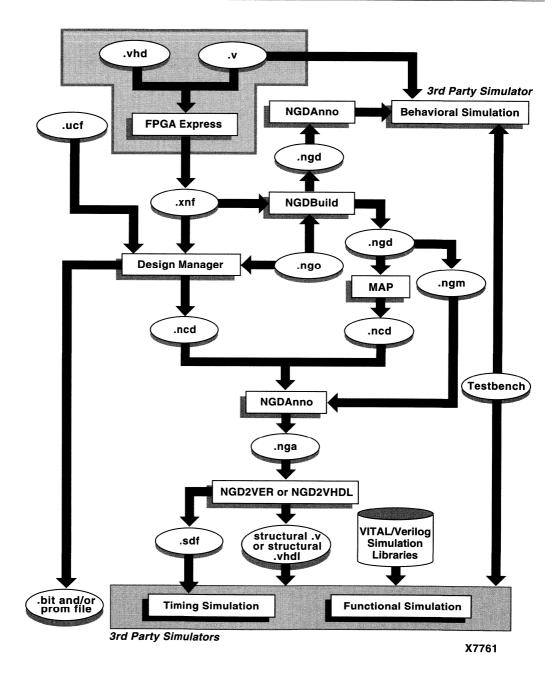

| Appendix B | FPGA Express Interface Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                   |

|            | Installation of FPGA Express  Design Entry With FPGA Express  Simulation With FPGA Express  Documentation  FPGA Express/XC4000EX Pre-Release Design Flow  Timing Constraints  Porting Code from FPGA Compiler to FPGA Express                                                                                                                                                                                                                                                                                               | B-2<br>B-2<br>B-3<br>B-3<br>B-3                                                                   |

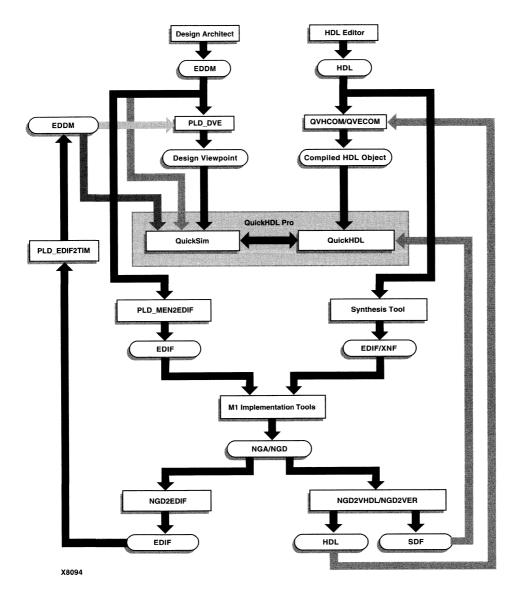

| Appendix C | Mentor Graphics Interface Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                   |

|            | Documentation  Setting up the Xilinx/Mentor Interface  Mentor/M1 Software Design Flow  Translating a Design to Xilinx EDIF  Timing Simulation  Generating a Timing-Annotated EDIF Netlist  Generating a Timing Model                                                                                                                                                                                                                                                                                                        | C-2<br>C-3<br>C-6<br>C-6<br>C-6                                                                   |

| Annondiy D | Creating a Simulation Viewpoint  Running PLD_QuickSim  Mentor-Related Environment Variables  Library Locations and Sample MGC Location Map.  Pin Locking  Timing Constraints                                                                                                                                                                                                                                                          | C-7<br>C-7<br>C-8<br>C-8                                                           |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

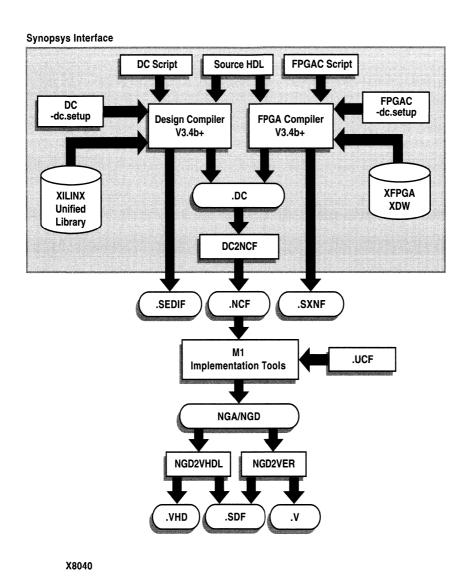

| Appendix D | Synopsys Interface Notes  Documentation                                                                                                                                                                                                                                                                                                                                                                                               | D-1                                                                                |

|            | Setting Up the Xilinx/Synopsys Interface Synopsys/M1 Software Design Flow Examples of Synopsys Setup Files .synopsys_dc.setup .synopsys_vss.setup Example Script File Timing Constraints and DC2NCF DC2NCF Design Flow FPGA Compiler Users Entity Coding Examples VHDL Code Verilog Code: Module Example Comments About Code                                                                                                          | D-3<br>D-3<br>D-6<br>D-7<br>D-9<br>D-10<br>D-10<br>D-10<br>D-13                    |

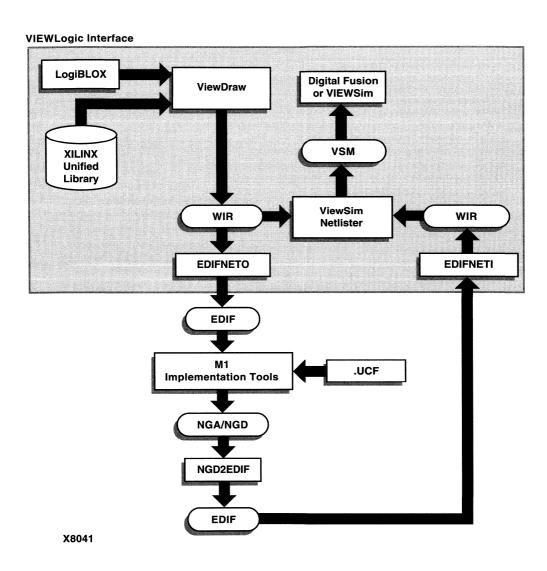

| Appendix E | Viewlogic Interface Notes                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                    |

|            | Documentation Setting Up Viewlogic Interface on Workstations Setting Up Xilinx/Viewlogic Interface on the PC Viewlogic/M1 Software Design Flow Setting Up Project Libraries On Workstations Xilinx Commands in ViewDraw On PCs Xilinx Commands in ViewDraw Assigning a Pin Location Timing Constraints Using Special XC4000EX Features Global Clock Buffers IOB Fast Capture Latches Output Multiplexer/2-Input Functions CLB Latches | E-1<br>E-3<br>E-4<br>E-6<br>E-7<br>E-7<br>E-8<br>E-8<br>E-9<br>E-9<br>E-10<br>E-10 |

| Appendix F | LogiBLOX                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                    |

|                                     | Documentation                                                                                                                                                                                                                                                                                                                                                                                                   | F-1                                                                                                   |  |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--|

|                                     | Setting Up LogiBLOX on a Workstation                                                                                                                                                                                                                                                                                                                                                                            | F-2                                                                                                   |  |

|                                     | Mentor Interface Environment Variables                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                       |  |

|                                     | Synopsys Interface Environment Variables                                                                                                                                                                                                                                                                                                                                                                        | F-2                                                                                                   |  |

|                                     | Viewlogic Interface Environment Variables                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                       |  |

|                                     | Setting Up LogiBLOX on a PC                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                       |  |

|                                     | Viewlogic Interface Environment Variables                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                       |  |

|                                     | Starting LogiBLOX                                                                                                                                                                                                                                                                                                                                                                                               | F-4                                                                                                   |  |

| Using LogiBLOX for Schematic Design |                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                       |  |

| Creating a LogiBLOX Module          |                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                       |  |

| Design simulation                   |                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                       |  |

| Copying Modules                     |                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                       |  |

|                                     | Using LogiBLOX for HDL Synthesis Design                                                                                                                                                                                                                                                                                                                                                                         | F-6                                                                                                   |  |

|                                     | Instantiating a LogiBLOX Module                                                                                                                                                                                                                                                                                                                                                                                 | F-6                                                                                                   |  |

|                                     | Analyzing a LogiBLOX Module                                                                                                                                                                                                                                                                                                                                                                                     | F-6                                                                                                   |  |

|                                     | Mentor QuickHDL                                                                                                                                                                                                                                                                                                                                                                                                 | F-7                                                                                                   |  |

|                                     | Synopsys VSS                                                                                                                                                                                                                                                                                                                                                                                                    | F-7                                                                                                   |  |

|                                     | Viewlogic Vantage                                                                                                                                                                                                                                                                                                                                                                                               | F-7                                                                                                   |  |

|                                     | LogiBLOX Modules                                                                                                                                                                                                                                                                                                                                                                                                | F-8                                                                                                   |  |

| Appendix G                          | Instantiated Components                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                       |  |

|                                     | STARTUP Component                                                                                                                                                                                                                                                                                                                                                                                               | G-1                                                                                                   |  |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                       |  |

|                                     | •                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                       |  |

|                                     | BSCAN Component                                                                                                                                                                                                                                                                                                                                                                                                 | G-2                                                                                                   |  |

|                                     | •                                                                                                                                                                                                                                                                                                                                                                                                               | G-2<br>G-3                                                                                            |  |

|                                     | BSCAN Component                                                                                                                                                                                                                                                                                                                                                                                                 | G-2<br>G-3<br>G-4                                                                                     |  |

|                                     | BSCAN Component  READBACK Component  RAM and ROM  Global Buffers                                                                                                                                                                                                                                                                                                                                                | G-2<br>G-3<br>G-4<br>G-5                                                                              |  |

|                                     | BSCAN Component                                                                                                                                                                                                                                                                                                                                                                                                 | G-2<br>G-3<br>G-4<br>G-5<br>G-7                                                                       |  |

| Appendix H                          | BSCAN Component  READBACK Component  RAM and ROM  Global Buffers  Fast Output Primitives                                                                                                                                                                                                                                                                                                                        | G-2<br>G-3<br>G-4<br>G-5<br>G-7                                                                       |  |

| Appendix H                          | BSCAN Component READBACK Component RAM and ROM Global Buffers Fast Output Primitives IOB Components  M1 Constraints Guide                                                                                                                                                                                                                                                                                       | G-2<br>G-3<br>G-4<br>G-5<br>G-7<br>G-8                                                                |  |

| Appendix H                          | BSCAN Component  READBACK Component  RAM and ROM  Global Buffers  Fast Output Primitives  IOB Components  M1 Constraints Guide  Constraint Entry Mechanisms                                                                                                                                                                                                                                                     | G-2<br>G-3<br>G-4<br>G-5<br>G-7<br>G-8                                                                |  |

| Appendix H                          | BSCAN Component READBACK Component RAM and ROM Global Buffers Fast Output Primitives IOB Components  M1 Constraints Guide  Constraint Entry Mechanisms Translating and Merging Logical Designs                                                                                                                                                                                                                  | G-2<br>G-3<br>G-4<br>G-5<br>G-7<br>G-8<br>H-1<br>H-3                                                  |  |

| Appendix H                          | BSCAN Component  READBACK Component  RAM and ROM  Global Buffers  Fast Output Primitives  IOB Components  M1 Constraints Guide  Constraint Entry Mechanisms                                                                                                                                                                                                                                                     | G-2<br>G-3<br>G-4<br>G-5<br>G-7<br>G-8<br>H-1<br>H-3<br>H-4                                           |  |

| Appendix H                          | BSCAN Component READBACK Component RAM and ROM Global Buffers Fast Output Primitives IOB Components  M1 Constraints Guide  Constraint Entry Mechanisms Translating and Merging Logical Designs Constraints File Overview                                                                                                                                                                                        | G-2<br>G-3<br>G-4<br>G-5<br>G-7<br>G-8<br>H-1<br>H-3<br>H-4<br>H-4                                    |  |

| Appendix H                          | BSCAN Component READBACK Component RAM and ROM Global Buffers Fast Output Primitives IOB Components  M1 Constraints Guide  Constraint Entry Mechanisms Translating and Merging Logical Designs Constraints File Overview The Netlist Constraint File (NCF)                                                                                                                                                      | G-2<br>G-3<br>G-4<br>G-5<br>G-7<br>G-8<br>H-1<br>H-3<br>H-4<br>H-4<br>H-5                             |  |

| Appendix H                          | BSCAN Component READBACK Component RAM and ROM Global Buffers Fast Output Primitives IOB Components  M1 Constraints Guide  Constraint Entry Mechanisms Translating and Merging Logical Designs Constraints File Overview The Netlist Constraint File (NCF) The User Constraint File (UCF)                                                                                                                       | G-2<br>G-3<br>G-4<br>G-5<br>G-7<br>G-8<br>H-1<br>H-3<br>H-4<br>H-4<br>H-5<br>H-5                      |  |

| Appendix H                          | BSCAN Component READBACK Component RAM and ROM Global Buffers Fast Output Primitives IOB Components  M1 Constraints Guide  Constraint Entry Mechanisms Translating and Merging Logical Designs Constraints File Overview The Netlist Constraint File (NCF) The User Constraint File (UCF) The Physical Constraints File (PCF) Case Sensitivity UCF Timing Constraints                                           | G-2<br>G-3<br>G-4<br>G-5<br>G-7<br>G-8<br>H-1<br>H-3<br>H-4<br>H-5<br>H-5<br>H-6<br>H-6               |  |

| Appendix H                          | BSCAN Component READBACK Component RAM and ROM Global Buffers Fast Output Primitives IOB Components  M1 Constraints Guide  Constraint Entry Mechanisms Translating and Merging Logical Designs Constraints File Overview The Netlist Constraint File (NCF) The User Constraint File (UCF) The Physical Constraints File (PCF) Case Sensitivity UCF Timing Constraints The "From:To" Style Timespec              | G-2<br>G-3<br>G-4<br>G-5<br>G-7<br>G-8<br>H-1<br>H-3<br>H-4<br>H-5<br>H-6<br>H-6<br>H-6               |  |

| Appendix H                          | BSCAN Component READBACK Component RAM and ROM Global Buffers Fast Output Primitives IOB Components  M1 Constraints Guide  Constraint Entry Mechanisms Translating and Merging Logical Designs Constraints File Overview The Netlist Constraint File (NCF) The User Constraint File (UCF) The Physical Constraints File (PCF) Case Sensitivity UCF Timing Constraints The "From:To" Style Timespec Using TPSYNC | G-2<br>G-3<br>G-4<br>G-5<br>G-7<br>G-8<br>H-1<br>H-3<br>H-4<br>H-5<br>H-6<br>H-6<br>H-6<br>H-8        |  |

| Appendix H                          | BSCAN Component READBACK Component RAM and ROM Global Buffers Fast Output Primitives IOB Components  M1 Constraints Guide  Constraint Entry Mechanisms Translating and Merging Logical Designs Constraints File Overview The Netlist Constraint File (NCF) The User Constraint File (UCF) The Physical Constraints File (PCF) Case Sensitivity UCF Timing Constraints The "From:To" Style Timespec              | G-2<br>G-3<br>G-4<br>G-5<br>G-7<br>G-8<br>H-1<br>H-3<br>H-4<br>H-5<br>H-6<br>H-6<br>H-6<br>H-8<br>H-9 |  |

|   | Ignoring Paths                                         | H-11 |

|---|--------------------------------------------------------|------|

|   | Controlling Skew                                       | H-12 |

|   | Constraint Precedence                                  | H-12 |

| L | ayout Constraints                                      | H-14 |

|   | Converting a Logical Design to a Physical Design       | H-14 |

|   | Last One Wins Resolution                               |      |

|   | XC5200 Constraints                                     | H-15 |

| Ε | fficient Use of Timespecs and Layout Constraints       | H-16 |

|   | The "Starter Set" of Timing Constraints                | H-16 |

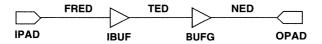

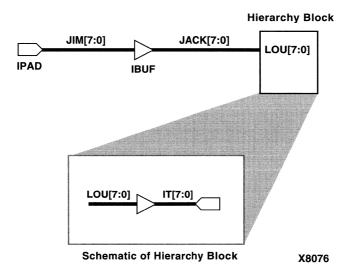

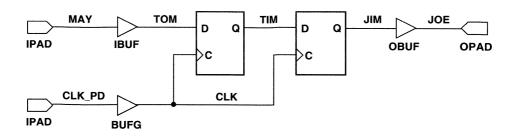

| S | tandard Block Delay Symbols                            | H-18 |

|   | able of M1-Supported Constraints                       |      |

| В | asic UCF Syntax Examples                               | H-22 |

|   | PERIOD TIMESPEC                                        | H-22 |

|   | FROM:TO TIMESPECs                                      | H-22 |

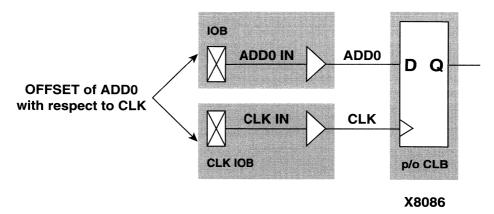

|   | OFFSET TIMESPEC                                        | H-23 |

|   | TIMING IGNORE                                          |      |

|   | PATH EXCEPTIONS                                        |      |

|   | MISCELLANEOUS EXAMPLES                                 |      |

| C | Constraining LogiBLOX RAM/ROM with Synopsys            | H-25 |

|   | Referencing a LogiBLOX Module/Component in the         |      |

|   | FPGA/Design Compiler and FPGA Express Flow             | H-26 |

|   | Referencing the Primitives of a LogiBLOX Module in the |      |

|   | FPGA/Design Compiler and FPGA Express Flow             |      |

|   | FPGA/Design Compiler and Express Verilog Example       | H-28 |

|   | test.v:                                                | H-28 |

|   | inside.v:                                              |      |

|   | memory.v (FPGA/Design compiler only)                   |      |

|   | runscript (FPGA/Design compiler only)                  |      |

|   | test.ucf (FPGA/Design compiler only)                   |      |

|   | test.ucf (FPGA Express only)                           |      |

|   | FPGA/Design Compiler and Express VHDL Example          |      |

|   | test.vhd                                               |      |

|   | inside.vhd                                             |      |

|   | runscript (FPGA/Design compiler only)                  |      |

|   | test.ucf (FPGA/Design compiler only)                   |      |

|   | test.ucf (FPGA Express only)                           | H-32 |

| C | Glossary                                               |      |

|   | Definitions                                            | 1 1  |

| L | aliases                                                |      |

|   | attribute                                              |      |

|   | AutoRoute                                              |      |

|   |                                                        |      |

Appendix I

| block                                                                                                                                                                           | 1-1                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| component                                                                                                                                                                       | 1-1                                                                |

| constraint                                                                                                                                                                      |                                                                    |

| Core Technology Tools                                                                                                                                                           |                                                                    |

| DC2NCF                                                                                                                                                                          | 1-2                                                                |

| guided mapping                                                                                                                                                                  | 1-2                                                                |

| HDL                                                                                                                                                                             |                                                                    |

| LCA file                                                                                                                                                                        |                                                                    |

| LCA2NCD                                                                                                                                                                         |                                                                    |

| LogiBLOX                                                                                                                                                                        | I-3                                                                |

| locking                                                                                                                                                                         | 1-3                                                                |

| logic                                                                                                                                                                           |                                                                    |

| Logic Block Editor                                                                                                                                                              | I-3                                                                |

| macro                                                                                                                                                                           |                                                                    |

| MCS file                                                                                                                                                                        |                                                                    |

| MDF file                                                                                                                                                                        |                                                                    |

| MRP file                                                                                                                                                                        |                                                                    |

| NCD file                                                                                                                                                                        |                                                                    |

| NCF file                                                                                                                                                                        | I-4                                                                |

|                                                                                                                                                                                 |                                                                    |

|                                                                                                                                                                                 |                                                                    |

| NGDAnno                                                                                                                                                                         |                                                                    |

| NGA file                                                                                                                                                                        | I-5                                                                |

| NGA fileNGD2EDIF                                                                                                                                                                | I-5<br>I-5                                                         |

| NGA file<br>NGD2EDIF<br>NGD2XNF                                                                                                                                                 | I-5<br>I-5<br>I-5                                                  |

| NGA file<br>NGD2EDIF<br>NGD2XNF<br>NGD2VER                                                                                                                                      | I-5<br>I-5<br>I-5<br>I-5                                           |

| NGA fileNGD2EDIFNGD2XNFNGD2VERNGD2VHDL                                                                                                                                          | I-5<br>I-5<br>I-5<br>I-5<br>I-5                                    |

| NGA fileNGD2EDIFNGD2XNFNGD2VERNGD2VHDLNGDBuild                                                                                                                                  | I-5<br>I-5<br>I-5<br>I-5<br>I-5                                    |

| NGA fileNGD2EDIFNGD2XNFNGD2VERNGD2VHDLNGDBuildNGD file                                                                                                                          | I-5<br>I-5<br>I-5<br>I-5<br>I-5<br>I-6                             |

| NGA file                                                                                                                                                                        | I-5<br>I-5<br>I-5<br>I-5<br>I-5<br>I-6<br>I-6                      |

| NGA file                                                                                                                                                                        | I-5<br>I-5<br>I-5<br>I-5<br>I-6<br>I-6                             |

| NGA file NGD2EDIF NGD2XNF NGD2VER NGD2VHDL NGDBuild NGD file NGM file PAR (Place and Route) path delay                                                                          | I-5<br>I-5<br>I-5<br>I-5<br>I-6<br>I-6<br>I-6                      |

| NGA file NGD2EDIF NGD2XNF NGD2VER NGD2VHDL NGDBuild NGD file NGM file PAR (Place and Route) path delay PCF file                                                                 | I-5 I-5 I-5 I-6 I-6 I-6 I-6                                        |

| NGA file                                                                                                                                                                        | I-5<br>I-5<br>I-5<br>I-5<br>I-6<br>I-6<br>I-6<br>I-6               |

| NGA file NGD2EDIF NGD2XNF NGD2VER NGD2VHDL NGDBuild NGD file NGM file PAR (Place and Route) path delay PCF file physical Design Rule Check (DRC) physical macro                 | I-5<br>I-5<br>I-5<br>I-5<br>I-6<br>I-6<br>I-6<br>I-6<br>I-6        |

| NGA file NGD2EDIF NGD2XNF NGD2VER NGD2VHDL NGDBuild NGD file NGM file PAR (Place and Route) path delay PCF file physical Design Rule Check (DRC) physical macro                 | I-5<br>I-5<br>I-5<br>I-5<br>I-6<br>I-6<br>I-6<br>I-6<br>I-7<br>I-7 |

| NGA file NGD2EDIF NGD2XNF NGD2VER NGD2VHDL NGDBuild NGD file NGM file PAR (Place and Route) path delay PCF file physical Design Rule Check (DRC) physical macro pin             | I-5<br>I-5<br>I-5<br>I-5<br>I-6<br>I-6<br>I-6<br>I-7<br>I-7        |

| NGA file NGD2EDIF NGD2XNF NGD2VER NGD2VHDL NGDBuild NGD file NGM file PAR (Place and Route) path delay PCF file physical Design Rule Check (DRC) physical macro pinwires proute | I-5<br>I-5<br>I-5<br>I-5<br>I-6<br>I-6<br>I-6<br>I-7<br>I-7<br>I-7 |

| NGA file NGD2EDIF NGD2XNF NGD2VER NGD2VHDL NGDBuild NGD file NGM file PAR (Place and Route) path delay PCF file physical Design Rule Check (DRC) physical macro pin             | I-5<br>I-5<br>I-5<br>I-5<br>I-6<br>I-6<br>I-6<br>I-7<br>I-7<br>I-7 |

| TRCE     | 1-8 |

|----------|-----|

| TWR file |     |

| wire     | 1-8 |

| UCF file | 1-8 |

#### Chapter 1

#### Introduction

Version M1.3 software will henceforth be referred to as M1 Software. This chapter contains the following sections.

- "Introduction" section

- "M1 Software Supported Families" section

- "Supported Netlists" section

- "M1 Software Instruction Volumes" section

- "New and Enhanced Tools" section

- "Third Party Interfaces" section

#### Introduction

Welcome to Xilinx's newest software release, vM1.3, known as M1 Software. The following enhancements and additions, made possible through a new core design, provide development designers with an improved suite of tools for implementing Programmable Logic Devices (PLDs).

**Note:** Compatibility with previous XACT releases XNF and LCA logical and physical design files has been preserved. The M1 Software may be used with the Xilinx Foundation Series F2.1 tools.

#### **M1 Software Supported Families**

M1 Software supports the following families with earlier version compatibility: 4000E, 4000L, 7300, and 9500. Two new families are also supported by the M1 Software: 4000EX and 4000XL. For further details about earlier version compatibility, refer to the appropriate CDROM (supplied with your Xilinx software). Xilinx manuals are divided by subject matter, and more than several volumes can apply

to one or more products. Technical information is included in the Xilinx "Programmable Logic Data Book".

#### **Supported Netlists**

Refer to the following table for netlists supported by the M1 Software.

| Netlists | Variations                                   |            |  |

|----------|----------------------------------------------|------------|--|

| EDIF     | Multiple variations are accepted, including: |            |  |

|          | SEDIF<br>EDIF                                | EDN<br>EDF |  |

| XNF      | Multiple variations are accepted, including: |            |  |

|          | SXNF<br>XFF                                  | XNF<br>XTF |  |

**Note:** All designs must be created using the Xilinx Unified Libraries. A list of components is located in the "Libraries Guide".

#### **M1 Software Instruction Volumes**

For a more detailed listing of documentation on this software release, please refer to the on-line documentation shipped via enclosed CDROMs, or visit our Web site at http://www.xilinx.com

#### **New and Enhanced Tools**

New and enhanced design features included in the M1 Software are listed in the order in which their descriptions appear in this section.

- Design Manager

- Flow Engine

- LogiBLOX

- Netlist Support

- Timing Specification Performance

- Timing Analyzer

- Multi-Pass PAR

- Re-Entrant Routing

- Guide for Incremental Design Changes

- EPIC-the Physical Design Editor

- Hardware Debugger

- PROM File Formatter

#### **Design Manager**

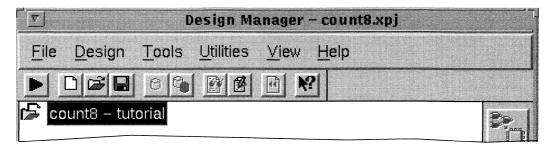

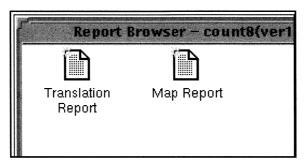

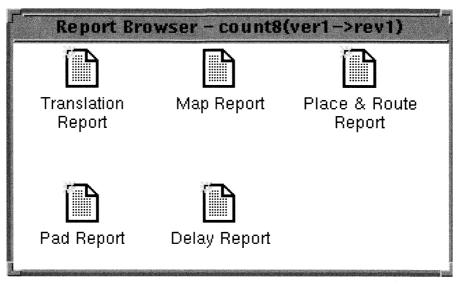

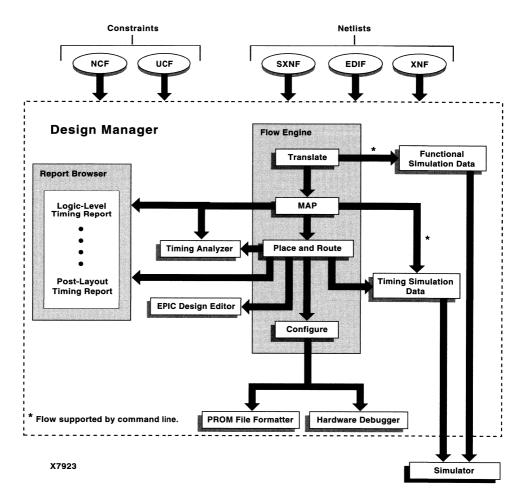

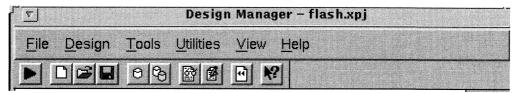

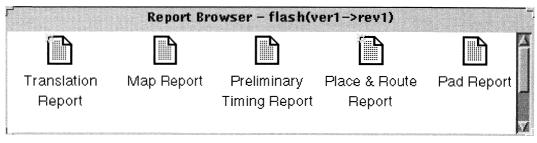

The Xilinx Design Manager is the graphical interface which manages the data file versions implemented during the design process. Results of these implementations are made available in reports and may be accessed through the Design Manager's Report Browser.

Design Manager also provides on-screen pushbutton access to the other Xilinx tools, such as the Flow Engine, Timing Analyzer, PROM File Formatter, EPIC Report Browser, and various navigation and information tools.

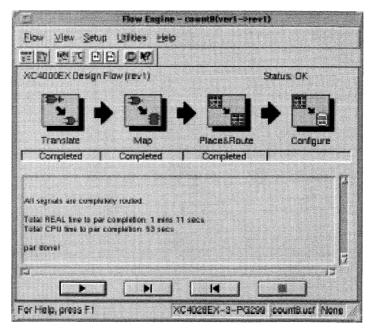

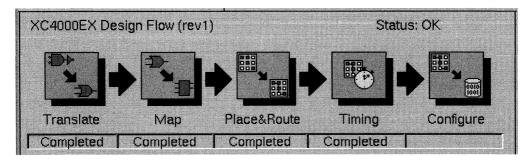

#### Flow Engine

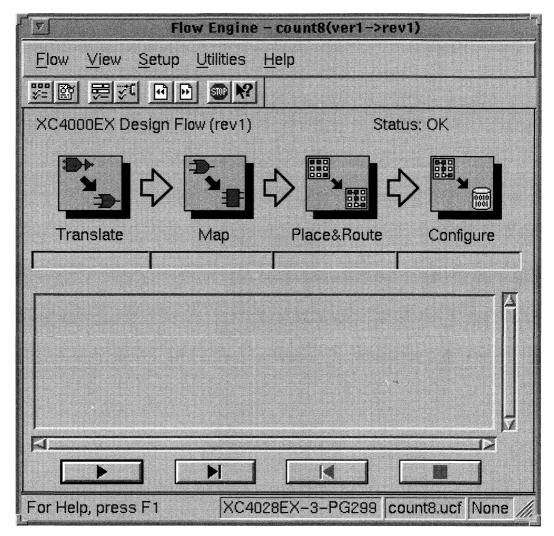

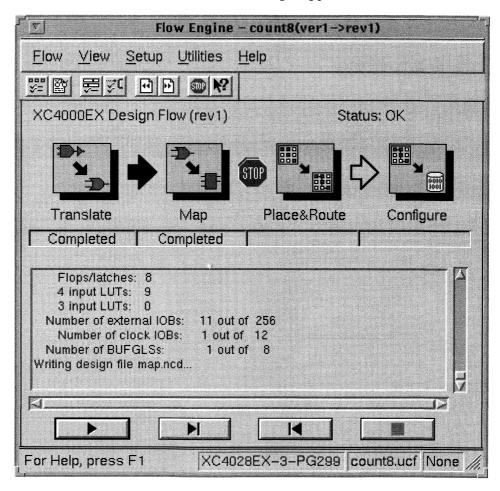

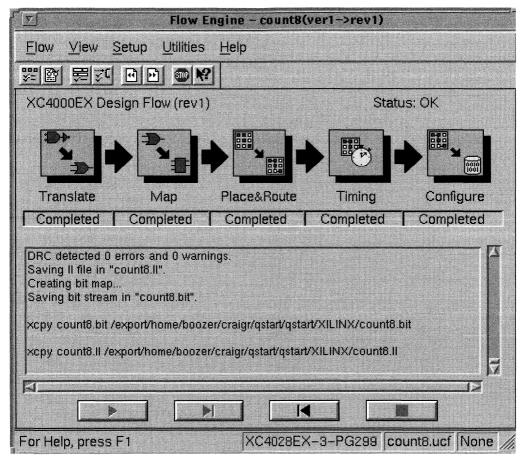

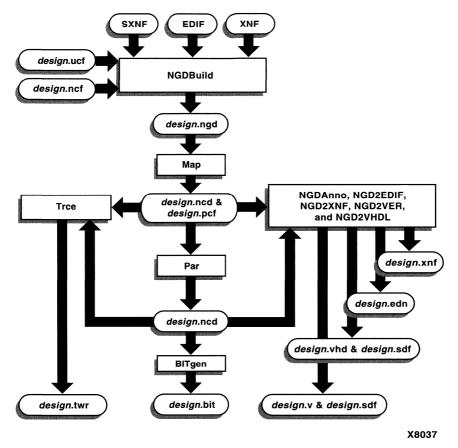

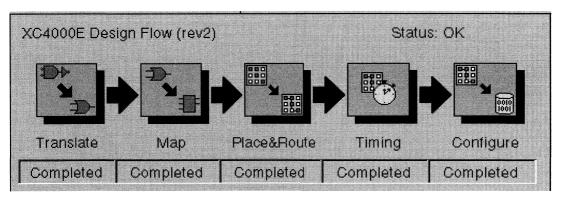

The Flow Engine displays and then executes all the steps needed to implement a Xilinx design. The Flow Engine:

- translates the design netlist

- maps the logic to CLBs

- places and routes the design

- creates a configuration file which downloads a design to a part.

- creates static timing reports and timing simulation netlists in the following formats: VHDL (Vital), Verilog, EDIF, or XNF

#### **LogiBLOX**

New in the M1 Software is LogiBLOX. The successor to X-BLOX, LogiBLOX can be used to create some of the following types of modules:

- ROMs

- RAMs

- counters

- comparators

- decoders

- modules for synthesis

- modules for schematic capture designs

- modules of behavioral simulation for fast functional simulation

LogiBLOX can be used as a stand-alone for synthesis designs and some schematic capture programs, or can be integrated with Viewlogic or Mentor Graphics schematic capture software. Refer to the "LogiBLOX" appendix for further details.

#### **Timing Specification Performance**

Xilinx M1 Software supports timing-driven placement and routing. The timing specification capability has been enhanced to incorporate greater precision. Features include

- new timing constraints

- implicit and explicit overrides of conflicting constraints

- override or overlap capability of constraints by slower or faster constraints that are either 1) narrower or 2) have a higher priority

#### **Timing Analyzer**

The Timing Analyzer produces a report on:

- overall design performance

- timing specifications performance

- specific path performance

Timing analysis can be performed on the block delays of a design directly out of MAP, or on the block and route delays of a design already placed and routed.

#### **Multi-Pass PAR**

The place and route (PAR) software allows multiple place and route iterations to be run:

- on a single machine

- on a UNIX network

on multiple machines in parallel

The multi-pass feature achieves optimum performance and efficiency, utilizing CPU time, instead of your time, to achieve faster design results.

#### **Re-Entrant Routing**

Once a place and route result is found that is close to meeting the desired specifications, notably those of timing, or is close to being completely routed, the implementation process can be re-entered to continue the routing process. This allows option and specification modifications during the routing stage of design implementation.

In addition to facilitating design changes, re-entrant routing significantly reduces CPU time of re-compiles.

#### **Guide for Incremental Design Changes**

Xilinx's Guide for Incremental Design Changes has been enhanced in the M1 Software to support guided mapping, and guided place and route functions.

Added to the guide in the M1 software is the Leverage Guide mode. This mode was specifically designed to accommodate the design iteration that requires more than minor changes, or the instance where a module has changed entirely due to the re-synthesis of your design.

#### **EPIC - Physical Design Editor**

Editor for Programmable Integrated Circuits (EPIC), a graphical editor, provides a view of the physical implementation of your Xilinx design. EPIC is new, and in function, a replacement for XDE/EDITLCA. Focus features of EPIC include:

- · Ability to view CLB mapping, placement and routing

- Timing analysis with critical paths highlighted

- Modification capability of the placement and routing of your Xilinx design

- Ability to create custom macros to be incorporated in your Xilinx design

#### **Hardware Debugger**

The Hardware Debugger downloads a configuration file to a single FPGA, or to a daisy chain of FPGAs through the Xchecker, Serial, or Parallel download cables. When used with the Xchecker cable, the Hardware Debugger can read back the state (logic levels) of the design signals inside the FPGA, and thus enable in-circuit design debugging.

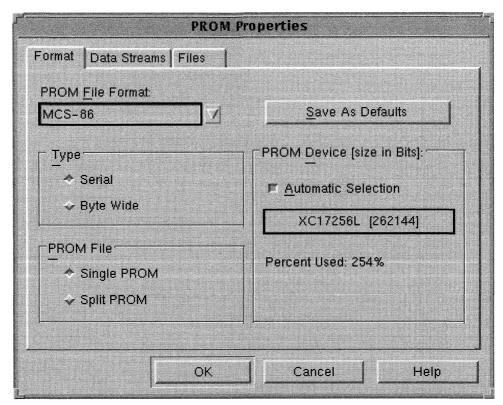

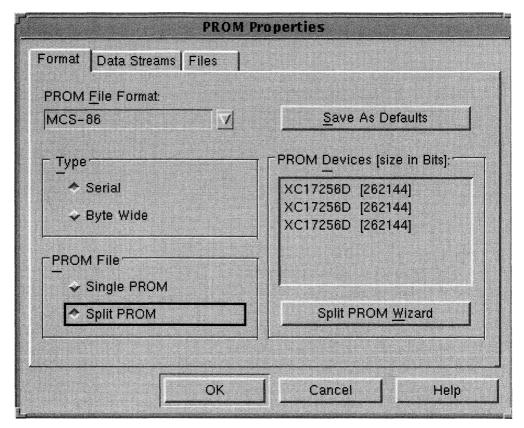

#### **PROM File Formatter**

PROM File Formatter creates files for serial or byte-wide configuration PROMs. Three formats are available: MCS, EXO, and TEK. The HEX format is also supported for microprocessor-based configuration.

#### **Third Party Interfaces**

For information on the following Xilinx supplied interface tools, refer to:

| Cadence         | Appendix A |

|-----------------|------------|

| FPGA Express    | Appendix B |

| Mentor Graphics | Appendix C |

| Synopsys        | Appendix D |

| Viewlogic       | Appendix E |

#### **Chapter 2**

#### Installation

This chapter contains the following sections.

- "Introduction" section

- "Obtaining and Setting Up Licenses" section

- "Customer Service" section

- "Registering and Licensing from the Web" section

- "Xilinx Web Licensing and Registration Program" section

- "Registering Via Telephone/Fax" section

- "M1 Requirements for Workstations" section

- "M1 Installation on Workstations" section

- "M1 Requirements for PCs" section

- "M1 Installation on PC" section

#### Introduction

Optimum use and operation of your M1 design tools is best guaranteed through correct installation of the M1 Software on recommended hardware, with recommended operating memory capacity. If you experience problems with either the installation, operation, or verification of your installation, please contact the Xilinx Technical Support hotline.

#### **Technical Support**

#### **Hotline Access**

| Location           | Telephone       | Electronic Mail     |

|--------------------|-----------------|---------------------|

| U.S. and Canada    | 1-800-255-7778  | hotline@xilinx.com  |

| Japan              | 81-33-297-9163  | jhotline@xilinx.com |

| France             | 33-1-3463-0100  | frhelp@xlinx.com    |

| Germany            | 49-89-9915-4930 | dlhelp@xilinx.com   |

| United Kingdom     | 44-1-932-820821 | ukhelp@xilinx.com   |

| To Contact Factory | 1-408-879-5199  | hotline@xilinx.com  |

Information is provided first for workstations; then, for PCs. The following licensing information applies to both workstation and PC users.

#### **Obtaining and Setting Up Licenses**

Before running your M1 Software, you will need to obtain a license from Xilinx. To obtain a license, you need to be a registered user in the Customer Service database. New Xilinx users should fill out their Xilinx registration card and **fax or mail** it to their Customer Service location or can register online. Customer Service will send your license and authorization codes in a *license.dat* file.

You can obtain a license by accessing the online Web tool or by contacting your local Xilinx Customer Service representative. If you request your license via fax, please fill out the "M1 License Request Form" figure 2-1 in this chapter.

**Note:** This form is also located in the front cover of your hardcopy version.

| M1 License R                                               | equest        | Form                 | <b>XILINX</b> <sup>®</sup> |  |

|------------------------------------------------------------|---------------|----------------------|----------------------------|--|

| Please complete and fax this to your local Xilinx Customer | form          | _                    |                            |  |

| Service representative.                                    |               | Xilinx End User Code |                            |  |

| End User Name                                              |               |                      |                            |  |

| Company                                                    |               |                      |                            |  |

| Shipping Address (Mailstop                                 | ) Do not u    | se P.O. Box          |                            |  |

| State/Province                                             |               | Zip/Postal Code      | Country                    |  |

| Telephone                                                  | FAX           |                      | E-Mail                     |  |

| Xilinx Product Part Number                                 |               | Serial/Key           | y Number                   |  |

| Ethernet Address/C-Drive Se                                | erial Number  | or Host ID & Serve   | er Name for Workstation    |  |

| Note: This form is also locate                             | d in the book | shelf box containing | your software and guides.  |  |

|                                                            |               |                      | X8089                      |  |

Figure 2-1 M1 License Request Form

#### **Customer Service**

Information for contacting your local Xilinx Customer Service representative.

#### **United States and Canada**

Monday-Friday, 8:00am to 5:00pm Pacific Standard Time 1-800-624-4782 and facsimile 408-559-0115.

#### **Europe**

Monday-Friday, 9:00am to 5:30 pm United Kingdom time - English speaking only.

| Country                  | Telephone        | Facsimile        |

|--------------------------|------------------|------------------|

| United Kingdom           | 01932-333550     | 01932-828521     |

| Belgium                  | 0800 73738       |                  |

| France                   | 0800 918333      |                  |

| Germany                  | 0130 816027      |                  |